# R1Q2A3636B/R1Q2A3618B/R1Q2A3609B

36-Mbit QDR™II SRAM 2-word Burst

> REJ03C0341-0003 Preliminary Rev. 0.03 Apr. 11, 2008

## **Description**

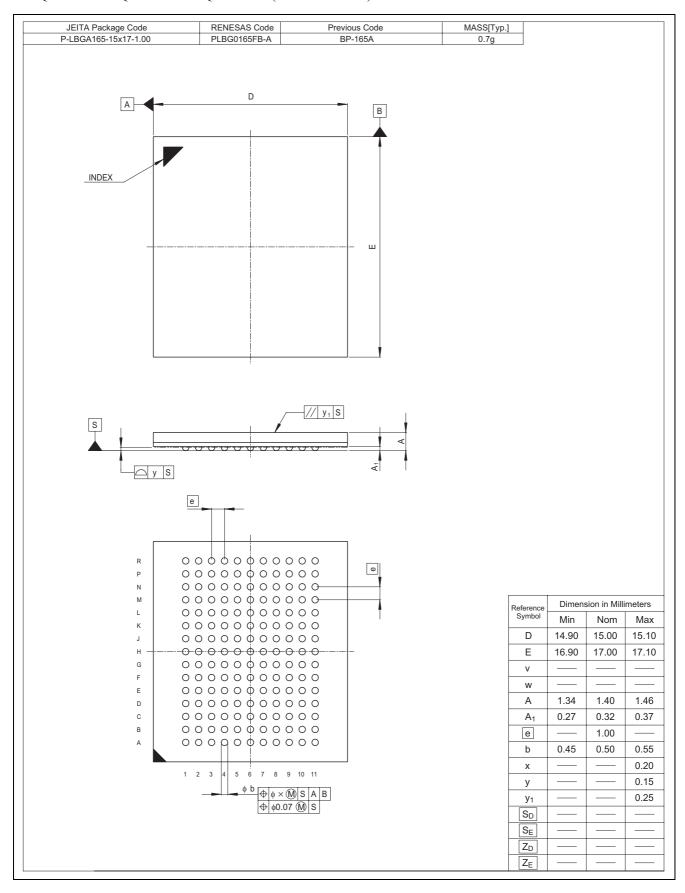

The R1Q2A3636B is a 1,048,576-word by 36-bit, the R1Q2A3618B is a 2,097,152-word by 18-bit, and the R1Q2A3609B is a 4,194,304-word by 9-bit synchronous quad data rate static RAM fabricated with advanced CMOS technology using full CMOS six-transistor memory cell. It integrates unique synchronous peripheral circuitry and a burst counter. All input registers controlled by an input clock pair (K and /K) and are latched on the positive edge of K and /K. These products are suitable for applications which require synchronous operation, high speed, low voltage, high density and wide bit configuration. These products are packaged in 165-pin plastic FBGA package.

#### **Features**

- 1.8 V  $\pm$  0.1 V power supply for core (V<sub>DD</sub>)

- 1.4 V to  $V_{DD}$  power supply for I/O ( $V_{DDO}$ )

- DLL circuitry for wide output data valid window and future frequency scaling

- Separate independent read and write data ports with concurrent transactions

- 100% bus utilization DDR read and write operation

- Two-tick burst for low DDR transaction size

- Two input clocks (K and /K) for precise DDR timing at clock rising edges only

- Two output clocks (C and /C) for precise flight time and clock skew matching-clock and data delivered together to receiving device

- Internally self-timed write control

- Clock-stop capability with µs restart

- User programmable impedance output

- Fast clock cycle time: 4.0 ns (250 MHz)/5.0 ns (200 MHz)/6.0 ns (167 MHz)

- Simple control logic for easy depth expansion

- JTAG boundary scan

Notes: QDR RAMs and Quad Data Rate RAMs comprise a new family of products developed by Cypress Semiconductor, IDT, NEC, Samsung, and Renesas Technology Corp.

Preliminary: The specifications of this device are subject to change without notice. Please contact your nearest

Renesas Technology's Sales Dept. regarding specifications.

# **Ordering Information**

|               | Part N           | umber                   | Organization            | Cycle   | Clock         | Package                      | Notes    |

|---------------|------------------|-------------------------|-------------------------|---------|---------------|------------------------------|----------|

|               |                  |                         |                         | time    | frequency     |                              |          |

| R1Q2A3636B    |                  |                         | 1-M word                | 4.0 ns  | 250 MHz       | Plastic FBGA 165-pin         |          |

| R1Q2A3636B    |                  |                         | × 36-bit                | 5.0 ns  | 200 MHz       | PLBG0165FB-A                 |          |

|               | R1Q2A3636BBG-60R |                         |                         | 6.0 ns  | 167 MHz       |                              |          |

|               | R1Q2A3618BBG-40R |                         | 2-M word                | 4.0 ns  | 250 MHz       |                              |          |

| R1Q2A3618B    | BG-50            | R                       | × 18-bit                | 5.0 ns  | 200 MHz       |                              |          |

| R1Q2A3618B    | BG-60            | R                       |                         | 6.0 ns  | 167 MHz       |                              |          |

| R1Q2A3609B    | BG-40            | R                       | 4-M word                | 4.0 ns  | 250 MHz       |                              |          |

| R1Q2A3609B    | BG-50            | R                       | × 9-bit                 | 5.0 ns  | 200 MHz       |                              |          |

| R1Q2A3609B    | BG-60            | R                       |                         | 6.0 ns  | 167 MHz       |                              |          |

| Notes:        |                  |                         |                         |         |               |                              |          |

| 1. Part No    | umber            |                         |                         |         |               |                              |          |

| (0:1)         | R1               | : Renesas Memory ¡      | : Renesas Memory prefix |         |               | : 1 <sup>st</sup> Generation |          |

| (2:3)         | Q2               | : QDRII 2-word Burs     | st SRAM                 |         | Α             | : 2 <sup>nd</sup> Generation |          |

|               | Q3               | : QDRII 4-word Burs     | t SRAM                  |         | В             | : 3 <sup>rd</sup> Generation |          |

|               | Q4               | : DDRII 2-word Burs     | t SRAM                  | (10:11) | BG            | : Package type=BGA           |          |

|               | Q5               | : DDRII 4-word Burs     | t SRAM                  | (12:13) | 60            | : Cycle time=6.0 ns          |          |

|               | Q6               | : DDRII 2-word Burs     | t SRAM                  |         | 50            | : Cycle time=5.0 ns          |          |

|               |                  | Separate I/O            |                         |         | 40            | : Cycle time=4.0 ns          |          |

| (4)           | Α                | : V <sub>DD</sub> =1.8V |                         |         | 33            | : Cycle time=3.3 ns          |          |

| (5:6)         | 36               | : Density = 36Mb        |                         | (14)    | R             | : Temperature range= 0°C     | ~70°C    |

|               | 72               | : Density = 72Mb        |                         |         | I             | : Temperature range= -40     | °C ~85°C |

| (7:8)         | 36               | : Organization = x36    |                         | (15)    | В             | : Pb-free                    |          |

|               | 18               | : Organization = x18    |                         |         | T             | : Tape&Reel                  |          |

|               | 09               | : Organization = x9     |                         |         | S             | : Pb-free and Tape&Reel      |          |

|               |                  |                         |                         |         | None          | : Standard (Pb and Tray)     |          |

|               |                  |                         |                         | (16)    | 0 ~9 , A ~Z   | :Renesas internal use        |          |

| 2. Marking Na | me               |                         |                         |         |               |                              |          |

|               |                  | Name(0:14) =Part Nu     |                         |         |               |                              |          |

| M             | larking          | Name(0:16) =Part Nu     | mber(0:14)+Bx           | Pt      | o-free (x=0 ~ | 9 , A ~Z)                    |          |

| (E            | Exampl           | e) R1Q2A3609BBG-6       |                         | . ~     |               |                              |          |

|               |                  | R1Q2A3609BBG-6          | 0RB0                    | Pb-free |               |                              |          |

## **Pin Arrangement**

## R1Q2A3636B series

|   | 1     | 2    | 3    | 4    | 5               | 6   | 7               | 8    | 9    | 10   | 11  |

|---|-------|------|------|------|-----------------|-----|-----------------|------|------|------|-----|

| Α | /CQ   | Vss  | NC   | /W   | /BW2            | /K  | /BW1            | /R   | SA   | NC   | CQ  |

| В | Q27   | Q18  | D18  | SA   | /BW3            | K   | /BW0            | SA   | D17  | Q17  | Q8  |

| С | D27   | Q28  | D19  | Vss  | SA              | SA  | SA              | Vss  | D16  | Q7   | D8  |

| D | D28   | D20  | Q19  | Vss  | Vss             | Vss | Vss             | Vss  | Q16  | D15  | D7  |

| Е | Q29   | D29  | Q20  | VDDQ | Vss             | Vss | Vss             | VDDQ | Q15  | D6   | Q6  |

| F | Q30   | Q21  | D21  | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | D14  | Q14  | Q5  |

| G | D30   | D22  | Q22  | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | Q13  | D13  | D5  |

| Н | /DOFF | VREF | VDDQ | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | VDDQ | VREF | ZQ  |

| J | D31   | Q31  | D23  | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | D12  | Q4   | D4  |

| K | Q32   | D32  | Q23  | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | Q12  | D3   | Q3  |

| L | Q33   | Q24  | D24  | VDDQ | Vss             | Vss | Vss             | VDDQ | D11  | Q11  | Q2  |

| М | D33   | Q34  | D25  | Vss  | Vss             | Vss | Vss             | Vss  | D10  | Q1   | D2  |

| N | D34   | D26  | Q25  | Vss  | SA              | SA  | SA              | Vss  | Q10  | D9   | D1  |

| Р | Q35   | D35  | Q26  | SA   | SA              | С   | SA              | SA   | Q9   | D0   | Q0  |

| R | TDO   | TCK  | SA   | SA   | SA              | /C  | SA              | SA   | SA   | TMS  | TDI |

(Top View)

## R1Q2A3618B series

|   | 1     | 2    | 3                | 4    | 5               | 6   | 7               | 8    | 9    | 10   | 11  |

|---|-------|------|------------------|------|-----------------|-----|-----------------|------|------|------|-----|

| Α | /CQ   | Vss  | SA               | /W   | /BW1            | /K  | NC              | /R   | SA   | NC   | CQ  |

| В | NC    | Q9   | D9               | SA   | NC              | K   | /BW0            | SA   | NC   | NC   | Q8  |

| С | NC    | NC   | D10              | Vss  | SA              | SA  | SA              | Vss  | NC   | Q7   | D8  |

| D | NC    | D11  | Q10              | Vss  | Vss             | Vss | Vss             | Vss  | NC   | NC   | D7  |

| Е | NC    | NC   | Q11              | VDDQ | Vss             | Vss | Vss             | VDDQ | NC   | D6   | Q6  |

| F | NC    | Q12  | D12              | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | NC   | NC   | Q5  |

| G | NC    | D13  | Q13              | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | NC   | NC   | D5  |

| Н | /DOFF | VREF | V <sub>DDQ</sub> | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | VDDQ | VREF | ZQ  |

| J | NC    | NC   | D14              | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | NC   | Q4   | D4  |

| K | NC    | NC   | Q14              | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | NC   | D3   | Q3  |

| L | NC    | Q15  | D15              | VDDQ | Vss             | Vss | Vss             | VDDQ | NC   | NC   | Q2  |

| М | NC    | NC   | D16              | Vss  | Vss             | Vss | Vss             | Vss  | NC   | Q1   | D2  |

| N | NC    | D17  | Q16              | Vss  | SA              | SA  | SA              | Vss  | NC   | NC   | D1  |

| Р | NC    | NC   | Q17              | SA   | SA              | С   | SA              | SA   | NC   | D0   | Q0  |

| R | TDO   | TCK  | SA               | SA   | SA              | /C  | SA              | SA   | SA   | TMS  | TDI |

(Top View)

## R1Q2A3636B/R1Q2A3618B/R1Q2A3609B

## R1Q2A3609B series

|   | 1     | 2    | 3                | 4    | 5               | 6   | 7               | 8    | 9    | 10   | 11  |

|---|-------|------|------------------|------|-----------------|-----|-----------------|------|------|------|-----|

| Α | /CQ   | Vss  | SA               | /W   | NC              | /K  | NC              | /R   | SA   | SA   | CQ  |

| В | NC    | NC   | NC               | SA   | NC              | K   | /BW             | SA   | NC   | NC   | Q4  |

| С | NC    | NC   | NC               | Vss  | SA              | SA  | SA              | Vss  | NC   | NC   | D4  |

| D | NC    | D5   | NC               | Vss  | Vss             | Vss | Vss             | Vss  | NC   | NC   | NC  |

| Е | NC    | NC   | Q5               | VDDQ | Vss             | Vss | Vss             | VDDQ | NC   | D3   | Q3  |

| F | NC    | NC   | NC               | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | NC   | NC   | NC  |

| G | NC    | D6   | Q6               | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | NC   | NC   | NC  |

| Н | /DOFF | VREF | V <sub>DDQ</sub> | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | VDDQ | VREF | ZQ  |

| J | NC    | NC   | NC               | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | NC   | Q2   | D2  |

| K | NC    | NC   | NC               | VDDQ | V <sub>DD</sub> | Vss | V <sub>DD</sub> | VDDQ | NC   | NC   | NC  |

| L | NC    | Q7   | D7               | VDDQ | Vss             | Vss | Vss             | VDDQ | NC   | NC   | Q1  |

| М | NC    | NC   | NC               | Vss  | Vss             | Vss | Vss             | Vss  | NC   | NC   | D1  |

| N | NC    | D8   | NC               | Vss  | SA              | SA  | SA              | Vss  | NC   | NC   | NC  |

| Р | NC    | NC   | Q8               | SA   | SA              | С   | SA              | SA   | NC   | D0   | Q0  |

| R | TDO   | TCK  | SA               | SA   | SA              | /C  | SA              | SA   | SA   | TMS  | TDI |

(Top View)

Notes: 1. Address expansion order for future higher density SRAMs (i.e.  $72Mb \rightarrow 144Mb \rightarrow 288Mb$ ):  $(9A \rightarrow 3A \rightarrow 10A) \rightarrow 2A \rightarrow 7A \rightarrow 5B$ .

## **Pin Description**

| Name                             | I/O type | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Notes |

|----------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| SA                               | Input    | Synchronous address inputs: These inputs are registered and must meet the setup and hold times around the rising edge of K for READ cycles and must meet the setup and hold times around the rising edge of /K for WRITE cycles. All transactions operate on a burst-of-two words (one clock period of bus activity). These inputs are ignored when device is deselected.                                                                                                                                                                                                                         |       |

| /R                               | Input    | Synchronous read: When low, this input causes the address inputs to be registered and a READ cycle to be initiated. This input must meet setup and hold times around the rising edge of K.                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| /W                               | Input    | Synchronous write: When low, this input causes the address inputs to be registered and a WRITE cycle to be initiated. This input must meet setup and hold times around the rising edge of K.                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| /BWx                             | Input    | Synchronous byte writes: When low, these inputs cause their respective byte to be registered and written during WRITE cycles. These signals must meet setup and hold times around the rising edges of K and /K for each of the two rising edges comprising the WRITE cycle. See Byte Write Truth Table for signal to data relationship.                                                                                                                                                                                                                                                           |       |

| K, /K                            | Input    | Input clock: This input clock pair registers address and control inputs on the rising edge of K, and registers data on the rising edge of K and the rising edge of /K. /K is ideally 180 degrees out of phase with K. All synchronous inputs must meet setup and hold times around the clock rising edges. These balls cannot remain $V_{\text{REF}}$ level.                                                                                                                                                                                                                                      |       |

| C, /C                            | Input    | Output clock: This clock pair provides a user-controlled means of tuning device output data. The rising edge of /C is used as the output timing reference for first output data. The rising edge of C is used as the output timing reference for second output data. Ideally, /C is 180 degrees out of phase with C. C and /C may be tied high to force the use of K and /K as the output reference clocks instead of having to provide C and /C clocks. If tied high, C and /C must remain high and not to be toggled during device operation. These balls cannot remain $V_{\text{REF}}$ level. |       |

| /DOFF                            | Input    | DLL disable: When low, this input causes the DLL to be bypassed for /DOFF Input stable, low frequency operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

| ZQ                               | Input    | Output impedance matching input: This input is used to tune the device outputs to the system data bus impedance. Q and CQ output impedance are set to $0.2 \times RQ$ , where RQ is a resistor from this ball to ground. This ball can be connected directly to $V_{DDQ}$ , which enables the minimum impedance mode. This ball cannot be connected directly to $V_{SS}$ or left unconnected.                                                                                                                                                                                                     |       |

| TMS<br>TDI                       | Input    | IEEE1149.1 test inputs: 1.8 V I/O levels. These balls may be left not TMS Input connected if the JTAG function is not used in the circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| TCK                              | Input    | IEEE1149.1 clock input: 1.8 V I/O levels. This ball must be tied to V <sub>SS</sub> if the JTAG function is not used TCK Input in the circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| D <sub>0</sub> to D <sub>n</sub> | Input    | Synchronous data inputs: Input data must meet setup and hold times around the rising edges of K and /K during WRITE operations. See Pin Arrangement figures for ball site location of individual signals.  The ×9 device uses D0 to D8. Remaining signals are not used.  The ×18 device uses D0 to D17. Remaining signals are not used.  The ×36 device uses D0 to D35.                                                                                                                                                                                                                           |       |

| CQ, /CQ                          | Output   | Synchronous echo clock outputs: The edges of these outputs are tightly matched to the synchronous data outputs and can be used as a data valid indication. These signals run freely and do not stop when Q tristates.                                                                                                                                                                                                                                                                                                                                                                             |       |

| TDO                              | Output   | IEEE 1149.1 test output: 1.8 V I/O level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| Q <sub>0</sub> to Q <sub>n</sub> | Output   | Synchronous data outputs: Output data is synchronized to the respective C and /C, or to the respective K and /K if C and /C are tied high. This bus operates in response to /R commands. See Pin Arrangement figures for ball site location of individual signals. The ×9 device uses Q0 to Q8. Remaining signals are not used. The ×18 device uses Q0 to Q17. Remaining signals are not used. The ×36 device uses Q0 to Q35.                                                                                                                                                                     |       |

| Name      | I/O type | Descriptions                                                                                                                                                              | Notes |

|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| $V_{DD}$  | Supply   | Power supply: 1.8 V nominal. See DC Characteristics and Operating V <sub>DD</sub> Supply Conditions for range.                                                            |       |

| $V_{DDQ}$ | Supply   | Power supply: Isolated output buffer supply. Nominally 1.5 V. 1.8 V is also permissible. See DC Characteristics and Operating Conditions for range.                       |       |

| $V_{SS}$  | Supply   | Power supply: Ground.                                                                                                                                                     |       |

| $V_{REF}$ | _        | HSTL input reference voltage: Nominally V <sub>DDQ</sub> /2, but may be adjusted to improve system noise margin. Provides a reference voltage for the HSTL input buffers. |       |

| NC        | _        | No connect: These signals are not internally connected. These signals can be left floating or connected to ground to improve package heat dissipation.                    |       |

Notes: 1. All power supply and ground balls must be connected for proper operation of the device.

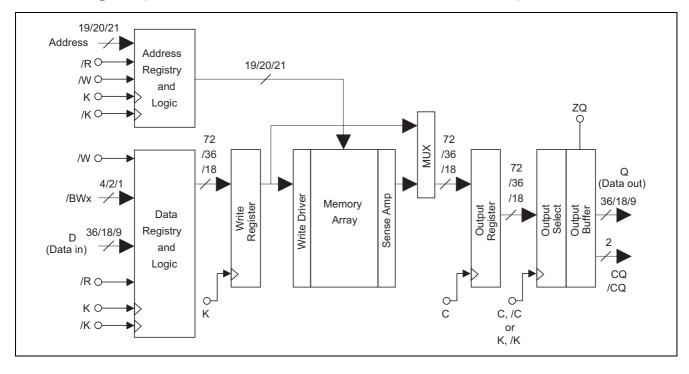

## Block Diagram (R1Q2A3636B / R1Q2A3618B / R1Q2A3609B series)

RENESAS

## **General Description**

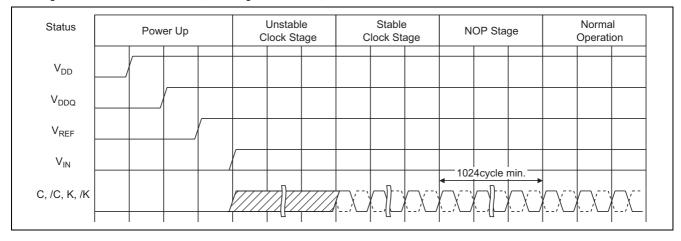

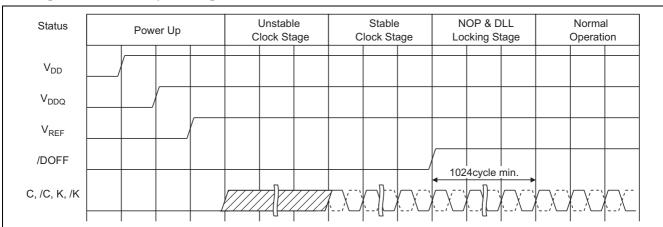

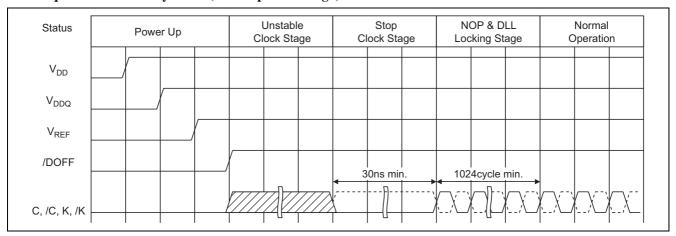

#### **Power-up and Initialization Sequence**

The following supply voltage application sequence is recommended:  $V_{SS}$ ,  $V_{DD}$ ,  $V_{DDQ}$ ,  $V_{REF}$  then  $V_{IN}$ .

After the stable power, there are three possible sequences.

- Sequence when DLL disable (/DOFF pin fixed low)

Just after the stable power and clock (K, /K, C, /C), 1024 NOP cycles (min.) are required for all operations, including JTAG functions, to become normal.

- 2a. Sequence controlled by /DOFF pin when DLL enable

Just after the stable power and clock (K, /K, C, /C), take /DOFF to be high.

The additional 1024 NOP cycles (min.) are required to lock the DLL and for all operations to become normal.

- 2b. Sequence controlled by Clock (/DOFF pin fixed high) when DLL enable If /DOFF pin is fixed high with unstable clock, the clock (K, /K, C, /C) must be stopped for 30ns (min.). During stop clock stage, C pin must tie low for 30 ns (min.). C, /C, K and /K cannot remain  $V_{REF}$  level. The additional 1024 NOP cycles (min.) are required to lock the DLL and for all operations to become normal.

- Notes: 1. After K or C clock is stopped, clock recovery cycles (1024 NOP cycles (min.)) are required for read/write operations to become normal.

- 2. When DLL is enable and the operating frequency is changed, DLL reset should be required again. After DLL reset again, the 1024 NOP cycles (min.) are needed to lock the DLL.

#### 1. Sequence when DLL disable (/DOFF pin fixed low)

## 2a. Sequence controlled by /DOFF pin when DLL enable

#### 2b. Sequence controlled by Clock (/DOFF pin fixed high) when DLL enable

#### **DLL Constraints**

- 1. DLL uses either K or C clock as its synchronizing input, the input should have low phase jitter which is specified as TKC var.

- 2. The lower end of the frequency at which the DLL can operate is 119MHz.

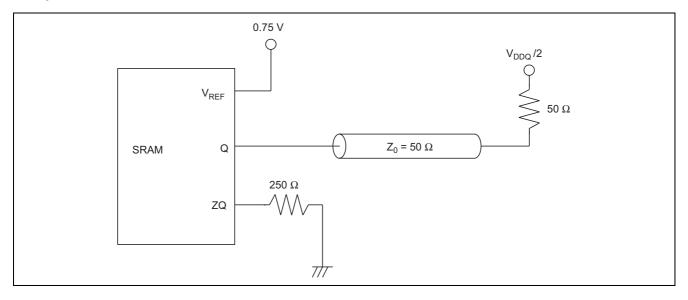

### **Programmable Output Impedance**

1. Output buffer impedance can be programmed by terminating the ZQ ball to Vss through a precision resistor (RQ). The value of RQ is five times the output impedance desired. The allowable range of RQ to guarantee impedance matching with a tolerance of 10% is  $250 \Omega$  typical.

The total external capacitance of ZQ ball must be less than 7.5 pF.

### **K Truth Table**

| Operation                         | K        | /R | /W | D or Q                       |          |         |  |

|-----------------------------------|----------|----|----|------------------------------|----------|---------|--|

| Write Cycle:                      | 1        | ×  | L  | Data in                      |          |         |  |

| Load address, input write data on |          |    |    | Input data                   | D(A+0)   | D(A+1)  |  |

| consecutive K and /K rising edges |          |    |    | Output clock                 | K(t)↑    | /K(t)↑  |  |

| Read Cycle:                       | <b>↑</b> | L  | ×  | Data out                     | Data out |         |  |

| Load address, output read data on |          |    |    | Output data                  | Q(A+0)   | Q(A+1)  |  |

| consecutive C and /C rising edges |          |    |    | Output clock                 | /C(t+1)↑ | C(t+2)↑ |  |

| NOP (No operation)                | <b>↑</b> | Н  | Н  | $D = \times$ or $Q = High-Z$ |          |         |  |

| Standby (Clock stopped)           | Stopped  | ×  | ×  | Previous state               |          |         |  |

Notes: 1. H: high level, L: low level, ×: don't care, ↑: rising edge.

- 2. Data inputs are registered at K and /K rising edges. Data outputs are delivered at C and /C rising edges, except if C and /C are high, then data outputs are delivered at K and /K rising edges.

- 3. /R and /W must meet setup/hold times around the rising edges (low to high) of K and are registered at the rising edge of K.

- 4. This device contains circuitry that will ensure the outputs will be in high-Z during power-up.

- 5. Refer to state diagram and timing diagrams for clarification.

- 6. When clocks are stopped, the following cases are recommended; the case of K = low, /K = high, C = low and /C = high, or the case of K = high, /K = low, C = high and /C = low. This condition is not essential, but permits most rapid restart by overcoming transmission line charging symmetrically.

## **Byte Write Truth Table (x36)**

| Operation        | K | /K | /BW0 | /BW1 | /BW2 | /BW3 |

|------------------|---|----|------|------|------|------|

| Write D0 to D35  | 1 | _  | L    | L    | L    | L    |

|                  | _ | 1  | L    | L    | L    | L    |

| Write D0 to D8   | 1 | _  | L    | Н    | Н    | Н    |

|                  | _ | 1  | L    | Н    | Н    | Н    |

| Write D9 to D17  | 1 | _  | Н    | L    | Н    | Н    |

|                  | _ | 1  | Н    | L    | Н    | Н    |

| Write D18 to D26 | 1 | _  | Н    | Н    | L    | Н    |

|                  | _ | 1  | Н    | Н    | L    | Н    |

| Write D27 to D35 | 1 | _  | Н    | Н    | Н    | L    |

|                  | _ | 1  | Н    | Н    | Н    | L    |

| Write nothing    | 1 | _  | Н    | Н    | Н    | Н    |

|                  | _ | 1  | Н    | Н    | Н    | Н    |

Notes: 1. H: high level, L: low level, ↑: rising edge.

2. Assumes a WRITE cycle was initiated. /BWx can be altered for any portion of the BURST WRITE operation provided that the setup and hold requirements are satisfied.

## **Byte Write Truth Table (x18)**

| Operation       | K | /K       | /BW0 | /BW1 |

|-----------------|---|----------|------|------|

| Write D0 to D17 | 1 | _        | L    | L    |

|                 |   | <b>↑</b> | L    | L    |

| Write D0 to D8  | 1 | _        | L    | Н    |

|                 | _ | 1        | L    | Н    |

| Write D9 to D17 | 1 | _        | Н    | L    |

|                 | _ | 1        | Н    | L    |

| Write nothing   | 1 | _        | Н    | Н    |

|                 | _ | 1        | Н    | Н    |

Notes: 1. H: high level, L: low level, ↑: rising edge.

2. Assumes a WRITE cycle was initiated. /BWx can be altered for any portion of the BURST WRITE operation provided that the setup and hold requirements are satisfied.

## **Byte Write Truth Table (x9)**

| Operation      | K | /K | /BW |

|----------------|---|----|-----|

| Write D0 to D8 | 1 | _  | L   |

|                | _ | 1  | L   |

| Write nothing  | 1 | _  | Н   |

|                | _ | 1  | Н   |

Notes: 1. H: high level, L: low level, ↑: rising edge.

2. Assumes a WRITE cycle was initiated. /BWx can be altered for any portion of the BURST WRITE operation provided that the setup and hold requirements are satisfied.

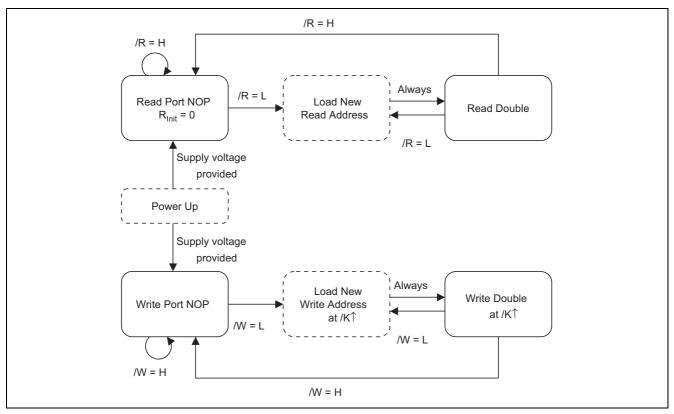

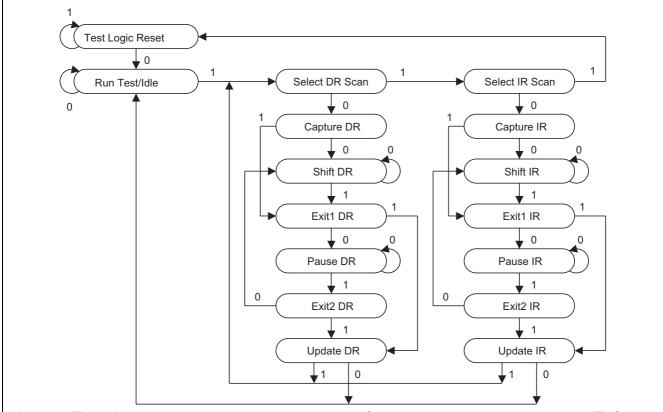

## **Bus Cycle State Diagram**

Notes: 1. The address is concatenated with one additional internal LSB to facilitate burst operation. The address order is always fixed as: xxx...xxx+0, xxx...xxx+1.

Bus cycle is terminated at the end of this sequence (burst count = 2).

- 2. Read and write state machines can be active simultaneously.

- 3. State machine control timing sequence is controlled by  ${\sf K}.$

## **Absolute Maximum Ratings**

| Parameter                 | Symbol           | Rating                                      | Unit | Notes |

|---------------------------|------------------|---------------------------------------------|------|-------|

| Input voltage on any ball | V <sub>IN</sub>  | -0.5 to V <sub>DD</sub> + 0.5 (2.5 V max.)  | V    | 1, 4  |

| Input/output voltage      | V <sub>I/O</sub> | -0.5 to V <sub>DDQ</sub> + 0.5 (2.5 V max.) | V    | 1, 4  |

| Core supply voltage       | $V_{DD}$         | −0.5 to 2.5                                 | V    | 1, 4  |

| Output supply voltage     | $V_{DDQ}$        | −0.5 to V <sub>DD</sub>                     | V    | 1, 4  |

| Junction temperature      | Tj               | +125 (max)                                  | °C   |       |

| Storage temperature       | T <sub>STG</sub> | −55 to +125                                 | °C   |       |

Notes: 1. All voltage is referenced to  $V_{\rm SS}$ .

- 2. Permanent device damage may occur if Absolute Maximum Ratings are exceeded. Functional operation should be restricted the Operation Conditions. Exposure to higher than recommended voltages for extended periods of time could affect device reliability.

- 3. These CMOS memory circuits have been designed to meet the DC and AC specifications shown in the tables after thermal equilibrium has been established.

- 4. The following supply voltage application sequence is recommended: V<sub>SS</sub>, V<sub>DD</sub>, V<sub>DDQ</sub>, V<sub>REF</sub> then V<sub>IN</sub>. Remember, according to the Absolute Maximum Ratings table, V<sub>DDQ</sub> is not to exceed 2.5 V, whatever the instantaneous value of V<sub>DDQ</sub>.

## **Recommended DC Operating Conditions**

$(Ta = 0 \text{ to } +70^{\circ}\text{C})$

| Parameter                  | Symbol               | Min                    | Тур  | Max                    | Unit | Notes |

|----------------------------|----------------------|------------------------|------|------------------------|------|-------|

| Power supply voltagecore   | $V_{DD}$             | 1.7                    | 1.8  | 1.9                    | V    |       |

| Power supply voltageI/O    | $V_{DDQ}$            | 1.4                    | 1.5  | $V_{DD}$               | V    |       |

| Input reference voltageI/O | $V_{REF}$            | 0.68                   | 0.75 | 0.95                   | V    | 1     |

| Input high voltage         | V <sub>IH (DC)</sub> | V <sub>REF</sub> + 0.1 | _    | $V_{DDQ} + 0.3$        | V    | 2, 3  |

| Input low voltage          | V <sub>IL (DC)</sub> | -0.3                   | _    | V <sub>REF</sub> – 0.1 | V    | 2, 3  |

Notes: 1. Peak to peak AC component superimposed on V<sub>REF</sub> may not exceed 5% of V<sub>REF</sub>.

2. Overshoot:  $V_{IH (AC)} \le V_{DDQ} + 0.5 V$  for  $t \le t_{KHKH}/2$

Undershoot:  $V_{IL\ (AC)} \ge -0.5\ V$  for  $t \le t_{KHKH}/2$

Power-up:  $V_{IH} \le V_{DDQ}$  + 0.3 V and  $V_{DD} \le 1.7$  V and  $V_{DDQ} \le 1.4$  V for  $t \le 200$  ms

During normal operation,  $V_{DDQ}$  must not exceed  $V_{DD}$ .

Control input signals may not have pulse widths less than  $t_{KHKL}$  (min) or operate at cycle rates less than  $t_{KHKH}$  (min).

During normal operation,  $V_{IH(DC)}$  must not exceed  $V_{DDQ}$  and  $V_{IL(DC)}$  must not be lower than  $V_{SS}$ .

3. These are DC test criteria. The AC V<sub>IH</sub> / V<sub>IL</sub> levels are defined separately to measure timing parameters.

### **DC Characteristics**

$(Ta = 0 \text{ to } +70^{\circ}\text{C}, V_{DD} = 1.8\text{V} \pm 0.1\text{V})$

|                              |                  |                  | -40 | -50 | -60 |      |         |

|------------------------------|------------------|------------------|-----|-----|-----|------|---------|

| Paramete                     | er               | Symbol           | Max | Max | Max | Unit | Notes   |

| Operating supply current     | (×9)             | I <sub>DD</sub>  | 600 | 550 | 500 | mA   | 1, 2, 3 |

| (READ / WRITE)               | (×18)            | I <sub>DD</sub>  | 650 | 600 | 550 | mA   | 1, 2, 3 |

|                              | (×36)            | I <sub>DD</sub>  | 700 | 650 | 600 | mA   | 1, 2, 3 |

| Standby supply current (NOP) | (×9 / ×18 / ×36) | I <sub>SB1</sub> | 350 | 340 | 330 | mA   | 2, 4, 5 |

#### R1Q2A3636B/R1Q2A3618B/R1Q2A3609B

| Parameter              | Symbol                | Min                       | Max                       | Unit | Test conditions               | Notes |

|------------------------|-----------------------|---------------------------|---------------------------|------|-------------------------------|-------|

| Input leakage current  | I <sub>LI</sub>       | -2                        | 2                         | μA   |                               | 10    |

| Output leakage current | I <sub>LO</sub>       | -5                        | 5                         | μA   |                               | 11    |

| Output high voltage    | V <sub>OH</sub> (Low) | V <sub>DDQ</sub> -0.2     | $V_{DDQ}$                 | V    | $ I_{OH}  \le 0.1 \text{ mA}$ | 8, 9  |

|                        | V <sub>OH</sub>       | V <sub>DDQ</sub> /2 -0.08 | V <sub>DDQ</sub> /2 +0.08 | V    | Note 6                        | 8, 9  |

| Output low voltage     | V <sub>OL</sub> (Low) | V <sub>SS</sub>           | 0.2                       | V    | $I_{OL} \le 0.1 \text{ mA}$   | 8, 9  |

|                        | V <sub>OL</sub>       | V <sub>DDQ</sub> /2 -0.08 | V <sub>DDQ</sub> /2 +0.08 | V    | Note 7                        | 8, 9  |

Notes: 1. All inputs (except ZQ,  $V_{REF}$ ) are held at either  $V_{IH}$  or  $V_{IL}$ .

- 2.  $I_{OUT} = 0$  mA.  $V_{DD} = V_{DD}$  max,  $t_{KHKH} = t_{KHKH}$  min.

- 3. Operating supply currents are measured at 100% bus utilization.

- 4. All address / data inputs are static at either  $V_{IN} > V_{IH}$  or  $V_{IN} < V_{IL}$ .

- 5. Reference value (Condition=NOP currents are valid when entering NOP after all pending READ and WRITE cycles are completed.)

- 6. Outputs are impedance-controlled.  $|I_{OH}| = (V_{DDQ}/2)/(RQ/5)$  for values of 175  $\Omega \le RQ \le 350 \Omega$ .

- 7. Outputs are impedance-controlled.  $I_{OL}$  =  $(V_{DDQ}/2)/(RQ/5)$  for values of 175  $\Omega \le RQ \le 350 \ \Omega$ .

- 8. AC load current is higher than the shown DC values. AC I/O curves are available upon request.

- 9. HSTL outputs meet JEDEC HSTL Class I standards.

- $10.0 \le V_{IN} \le V_{DDQ}$  for all input balls (except  $V_{REF}$ , ZQ, TCK, TMS, TDI ball).

- 11.  $0 \le V_{OUT} \le V_{DDQ}$  (except TDO ball), output disabled.

### **Thermal Resistance**

| Parameter           | Symbol            | Тур  | Unit | Notes |

|---------------------|-------------------|------|------|-------|

| Junction to Ambient | $	heta_{JA}$      | 24.5 | °C/W |       |

| Junction to Case    | $\theta_{\sf JC}$ | 5.6  | °C/W |       |

Note: These parameters are calculated under the condition of wind velocity = 1 m/s.

## Capacitance

$$(Ta = +25^{\circ}C, f=1.0MHz, V_{DD} = 1.8V, V_{DDO} = 1.5V)$$

| Parameter                           | Symbol           | Min | Тур | Max | Unit | Test conditions        | Notes |

|-------------------------------------|------------------|-----|-----|-----|------|------------------------|-------|

| Input capacitance                   | C <sub>IN</sub>  | _   | 2   | 3   | pF   | V <sub>IN</sub> = 0 V  | 1, 2  |

| Clock input capacitance             | C <sub>CLK</sub> | _   | 2   | 3   | pF   | V <sub>CLK</sub> = 0 V | 1, 2  |

| Input/output capacitance (D, Q, ZQ) | C <sub>I/O</sub> | _   | 3   | 4.5 | pF   | V <sub>I/O</sub> = 0 V | 1, 2  |

Notes: 1. These parameters are sampled and not 100% tested.

2. Except JTAG (TCK, TMS, TDI, TDO) pins.

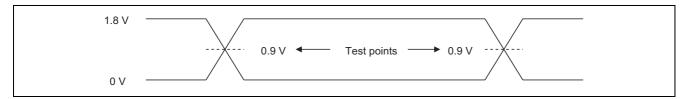

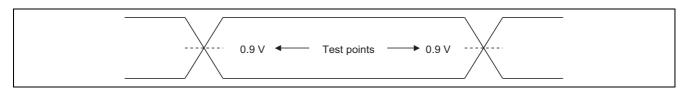

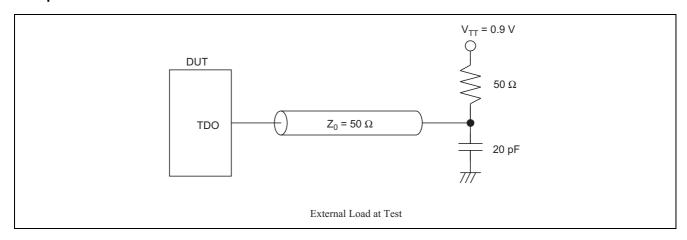

## **AC Test Conditions**

$$(Ta = 0 \text{ to } +70^{\circ}\text{C}, V_{DD} = 1.8\text{V} \pm 0.1\text{V})$$

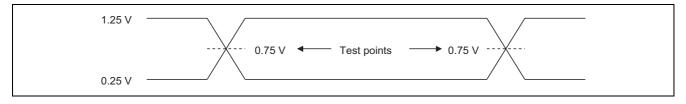

## Input waveform (Rise/fall time ≤ 0.3 ns)

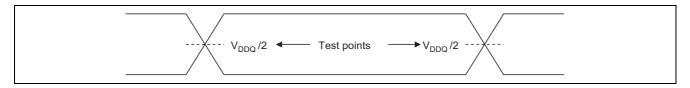

#### **Output waveform**

#### **Output load condition**

## **AC Operating Conditions**

| Parameter          | Symbol               | Min                    | Тур | Max                  | Unit | Notes      |

|--------------------|----------------------|------------------------|-----|----------------------|------|------------|

| Input high voltage | V <sub>IH (AC)</sub> | V <sub>REF</sub> + 0.2 |     | _                    | V    | 1, 2, 3, 4 |

| Input low voltage  | V <sub>IL (AC)</sub> |                        | _   | $V_{\text{REF}}-0.2$ | V    | 1, 2, 3, 4 |

Notes: 1. All voltages referenced to V<sub>SS</sub> (GND).

- 2. These conditions are for AC functions only, not for AC parameter test.

- 3. Overshoot:  $V_{IH (AC)} \le V_{DDQ} + 0.5 V$  for  $t \le t_{KHKH}/2$

Undershoot:  $V_{IL\ (AC)} \ge -0.5\ V$  for  $t \le t_{KHKH}/2$

Power-up:  $V_{IH} \leq V_{DDQ}$  + 0.3 V and  $V_{DD} \leq$  1.7 V and  $V_{DDQ} \leq$  1.4 V for  $t \leq$  200 ms

During normal operation,  $V_{DDQ}$  must not exceed  $V_{DD}$ . Control input signals may not have pulse widths less than  $t_{KHKL}$  (min) or operate at cycle rates less than  $t_{KHKH}$  (min).

- 4. To maintain a valid level, the transitioning edge of the input must:

- a. Sustain a constant slew rate from the current AC level through the target AC level,  $V_{IL\ (AC)}$  or  $V_{IH\ (AC)}$ .

RENESAS

- b. Reach at least the target AC level.

- c. After the AC target level is reached, continue to maintain at least the target DC level, V<sub>IL (DC)</sub> or V<sub>IH (DC)</sub>.

#### **AC Characteristics**

$(Ta = 0 \text{ to } +70^{\circ}\text{C}, V_{DD} = 1.8\text{V} \pm 0.1\text{V})$

|                                          |                       |       | 40   |       | 50   | -     | 60   |       |       |

|------------------------------------------|-----------------------|-------|------|-------|------|-------|------|-------|-------|

| Parameter                                | Symbol                | Min   | Max  | Min   | Max  | Min   | Max  | Unit  | Notes |

| Average clock cycle time (K, /K, C, /C)  | t <sub>KHKH</sub>     | 4.00  | 8.40 | 5.00  | 8.40 | 6.00  | 8.40 | ns    |       |

| Clock phase jitter<br>(K, /K, C, /C)     | t <sub>KC</sub> var   | _     | 0.20 | _     | 0.20 | _     | 0.20 | ns    | 3     |

| Clock high time<br>(K, /K, C, /C)        | t <sub>KHKL</sub>     | 1.60  | _    | 2.00  | _    | 2.40  | _    | ns    |       |

| Clock low time<br>(K, /K, C, /C)         | t <sub>KLKH</sub>     | 1.60  | _    | 2.00  | _    | 2.40  | _    | ns    |       |

| Clock to /clock<br>(K to /K, C to /C)    | t <sub>KH/KH</sub>    | 1.80  | _    | 2.20  | _    | 2.70  | _    | ns    |       |

| /Clock to clock<br>(/K to K, /C to C)    | t/kHKH                | 1.80  | _    | 2.20  | _    | 2.70  | _    | ns    |       |

| Clock to data clock (K to C, /K to /C)   | t <sub>KHCH</sub>     | 0     | 1.10 | 0     | 1.60 | 0     | 2.10 | ns    |       |

| DLL lock time (K, C)                     | t <sub>KC</sub> lock  | 1,024 | _    | 1,024 | _    | 1,024 | _    | Cycle | 2     |

| K static to DLL reset                    | t <sub>KC</sub> reset | 30    | _    | 30    | _    | 30    | _    | ns    | 7     |

| C, /C high to output valid               | t <sub>CHQV</sub>     | _     | 0.45 | _     | 0.45 | _     | 0.50 | ns    |       |

| C, /C high to output hold                | t <sub>CHQX</sub>     | -0.45 | _    | -0.45 | _    | -0.50 | _    | ns    |       |

| C, /C high to echo clock valid           | t <sub>CHCQV</sub>    | _     | 0.45 | _     | 0.45 | _     | 0.50 | ns    |       |

| C, /C high to echo clock hold            | t <sub>CHCQX</sub>    | -0.45 | _    | -0.45 | _    | -0.50 | _    | ns    |       |

| CQ, /CQ high to output valid             | t <sub>CQHQV</sub>    | _     | 0.30 | _     | 0.35 | _     | 0.40 | ns    | 4, 7  |

| CQ, /CQ high to output hold              | $t_{CQHQX}$           | -0.30 | _    | -0.35 | _    | -0.40 | _    | ns    | 4, 7  |

| C, /C high to output high-Z              | <b>t</b> chqz         |       | 0.45 |       | 0.45 |       | 0.50 | ns    | 5     |

| C, /C high to output low-Z               | t <sub>CHQX1</sub>    | -0.45 |      | -0.45 | _    | -0.50 |      | ns    | 5     |

| Address valid to K, /K rising edge       | t <sub>AVKH</sub>     | 0.35  |      | 0.40  | _    | 0.50  | _    | ns    | 1     |

| Control inputs valid to K rising edge    | t <sub>IVKH</sub>     | 0.35  | _    | 0.40  | _    | 0.50  | _    | ns    | 1     |

| Data-in valid to K, /K rising edge       | t <sub>DVKH</sub>     | 0.35  | _    | 0.40  | _    | 0.50  | _    | ns    | 1     |

| K, /K rising edge to address hold        | t <sub>KHAX</sub>     | 0.35  | _    | 0.40  | _    | 0.50  | _    | ns    | 1     |

| K, /K rising edge to control inputs hold | t <sub>KHIX</sub>     | 0.35  |      | 0.40  | —    | 0.50  | _    | ns    | 1     |

| K, /K rising edge to data-in hold        | t <sub>KHDX</sub>     | 0.35  |      | 0.40  | _    | 0.50  |      | ns    | 1     |

Notes: 1. This is a synchronous device. All addresses, data and control lines must meet the specified setup and hold times for all latching clock edges.

- 2. V<sub>DD</sub> slew rate must be less than 0.1 V DC per 50 ns for DLL lock retention. DLL lock time begins once V<sub>DD</sub> and input clock are stable. It is recommended that the device is kept inactive during these cycles.

- 3. Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.

- 4. Echo clock is very tightly controlled to data valid / data hold. By design, there is a ±0.1 ns variation from echo clock to data. The datasheet parameters reflect tester guardbands and test setup variations.

- 5. Transitions are measured ±100 mV from steady-state voltage.

- 6. At any given voltage and temperature t<sub>CHQZ</sub> is less than t<sub>CHQX1</sub> and t<sub>CHQZ</sub> less than t<sub>CHQY</sub>.

- 7. These parameters are sampled.

#### Remarks:

- 1. Test conditions as specified with the output loading as shown in AC Test Conditions unless otherwise noted.

- 2. Control input signals may not be operated with pulse widths less than t<sub>KHKL</sub> (min).

- 3. If C, /C are tied high, K, /K become the references for C, /C timing parameters.

- 4. V<sub>DDQ</sub> is +1.5 V DC.

- Control signals are /R, /W, /BW, /BW0, /BW1, /BW2 and /BW3. BWn signals must operate at the same timing as Data in.

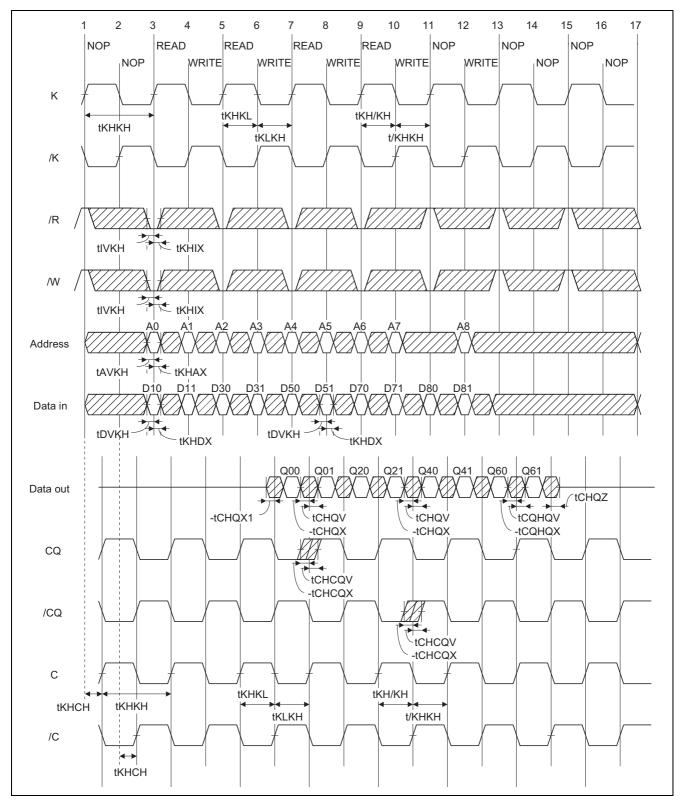

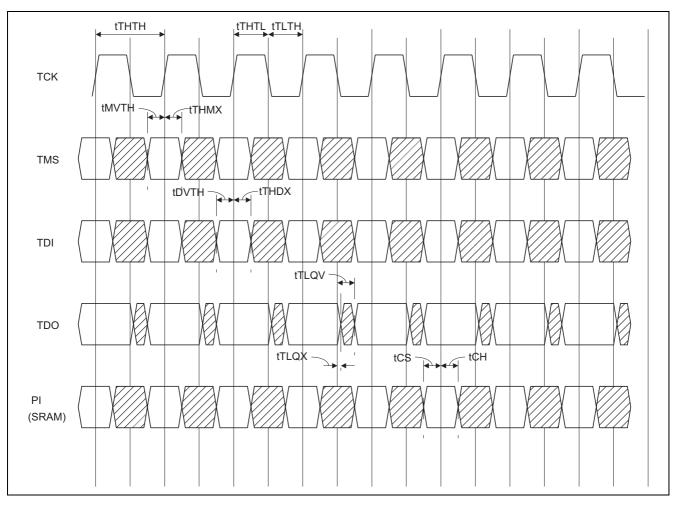

## **Timing Waveforms**

### **Read and Write Timing**

Notes: 1. Q00 refers to output from address A0+0. Q01 refers to output from the next internal burst address following A0, i.e., A0+1.

- 2. Outputs are disable (high-Z) one clock cycle after a NOP.

- 3. In this example, if address A0 = A1, then data Q00 = D10, Q01 = D11. Write data is forwarded immediately as read results.

- 4. To control read and write operations, /BW signals must operate at the same timing as Data in.

## **JTAG Specification**

These products support a limited set of JTAG functions as in IEEE standard 1149.1.

## **Disabling the Test Access Port**

It is possible to use this device without utilizing the TAP. To disable the TAP controller without interfering with normal operation of the device, TCK must be tied to  $V_{SS}$  to preclude mid level inputs. TDI and TMS are designed so an undriven input will produce a response identical to the application of a logic 1,and may be left unconnected. But they may also be tied to  $V_{DD}$  through a  $1k\Omega$  resistor.TDO should be left unconnected.

## **Test Access Port (TAP) Pins**

| Symbol I/O | Pin assignments | Description                                                                                                                                                                                                                                                             | Notes |

|------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| TCK        | 2R              | Test clock input. All inputs are captured on the rising edge of TCK and all outputs propagate from the falling edge of TCK.                                                                                                                                             |       |

| TMS        | 10R             | Test mode select. This is the command input for the TAP controller state machine.                                                                                                                                                                                       |       |

| TDI        | 11R             | Test data input. This is the input side of the serial registers placed between TDI and TDO. The register placed between TDI and TDO is determined by the state of the TAP controller state machine and the instruction that is currently loaded in the TAP instruction. |       |

| TDO        | 1R              | Test data output. Output changes in response to the falling edge of TCK. This is the output side of the serial registers placed between TDI and TDO.                                                                                                                    |       |

Notes: The device does not have TRST (TAP reset). The Test-Logic Reset state is entered while TMS is held high for five rising edges of TCK. The TAP controller state is also reset on SRAM POWER-UP.

## **TAP DC Operating Characteristics**

$(Ta = 0 \text{ to } +70^{\circ}\text{C}, V_{DD} = 1.8\text{V} \pm 0.1\text{V})$

| Parameter              | Symbol             | Min  | Тур | Max                   | Unit | Notes                                                                                   |

|------------------------|--------------------|------|-----|-----------------------|------|-----------------------------------------------------------------------------------------|

| Input high voltage     | V <sub>IH</sub>    | +1.3 | _   | V <sub>DD</sub> + 0.3 | V    |                                                                                         |

| Input low voltage      | V <sub>IL</sub>    | -0.3 | _   | +0.5                  | V    |                                                                                         |

| Input leakage current  | ILI                | -5.0 | _   | +5.0                  | μΑ   | $0 \text{ V} \leq V_{IN} \leq V_{DD}$                                                   |

| Output leakage current | I <sub>LO</sub>    | -5.0 | _   | +5.0                  | μΑ   | $\begin{array}{c} 0 \ V \leq V_{IN} \leq V_{DD}, \\ \text{output disabled} \end{array}$ |

| Output low voltage     | V <sub>OL1</sub>   | _    | _   | 0.2                   | V    | I <sub>OLC</sub> = 100 μA                                                               |

|                        | $V_{OL2}$          | _    | _   | 0.4                   | V    | I <sub>OLT</sub> = 2 mA                                                                 |

| Output high voltage    | V <sub>OH1</sub>   | 1.6  |     |                       | V    | I <sub>OHC</sub>   = 100 μA                                                             |

|                        | $V_{\mathrm{OH2}}$ | 1.4  | _   |                       | V    | I <sub>OHT</sub>   = 2 mA                                                               |

Notes: 1. All voltages referenced to V<sub>SS</sub> (GND).

- 2. Power-up:  $V_{IH} \le V_{DDQ} + 0.3 \text{ V}$  and  $V_{DD} \le +1.7 \text{ V}$  and  $V_{DDQ} \le +1.4 \text{ V}$  for  $t \le 200 \text{ ms}$ .

- 3. In "EXTEST" mode and "SAMPLE" mode,  $V_{\text{DDQ}}$  is nominally 1.5 V.

- 4. ZQ:  $V_{IH} = V_{DDQ}$ .

## **TAP AC Test Conditions**

| Parameter                                               | Symbol          | Conditions   | Unit | Notes |

|---------------------------------------------------------|-----------------|--------------|------|-------|

| Temperature                                             | Та              | 0 ≤ Ta ≤ +70 | °C   |       |

| Input timing measurement reference levels               | $V_{REF}$       | 0.9          | V    |       |

| Input pulse levels                                      | $V_{IL},V_{IH}$ | 0 to 1.8     | V    |       |

| Input rise/fall time                                    | tr, tf          | ≤ 1.0        | ns   |       |

| Output timing measurement reference levels              |                 | 0.9          | V    |       |

| Test load termination supply voltage (V <sub>TT</sub> ) |                 | 0.9          | V    |       |

| Output load                                             |                 | See figures  |      |       |

## Input waveform

## **Output waveform**

## **Output load condition**

RENESAS

## **TAP AC Operating Characteristics**

$(Ta = 0 \text{ to } +70^{\circ}\text{C}, V_{DD} = 1.8\text{V} \pm 0.1\text{V})$

| Parameter                    | Symbol            | Min | Тур | Max | Unit | Notes |

|------------------------------|-------------------|-----|-----|-----|------|-------|

| Test clock (TCK) cycle time  | t <sub>THTH</sub> | 100 | _   | _   | ns   |       |

| TCK high pulse width         | t <sub>THTL</sub> | 40  | _   | _   | ns   |       |

| TCK low pulse width          | t <sub>TLTH</sub> | 40  | _   | _   | ns   |       |

| Test mode select (TMS) setup | t <sub>MVTH</sub> | 10  | _   | _   | ns   |       |

| TMS hold                     | t <sub>THMX</sub> | 10  | _   | _   | ns   |       |

| Capture setup                | t <sub>CS</sub>   | 10  | _   | _   | ns   | 1     |

| Capture hold                 | t <sub>CH</sub>   | 10  | _   | _   | ns   | 1     |

| TDI valid to TCK high        | t <sub>DVTH</sub> | 10  | _   | _   | ns   |       |

| TCK high to TDI invalid      | t <sub>THDX</sub> | 10  | _   | _   | ns   |       |

| TCK low to TDO unknown       | t <sub>TLQX</sub> | 0   | _   | _   | ns   |       |

| TCK low to TDO valid         | t <sub>TLQV</sub> | _   | _   | 20  | ns   |       |

Notes: 1.  $t_{CS}$  +  $t_{CH}$  defines the minimum pause in RAM I/O pad transitions to assure pad data capture.

## **TAP Controller Timing Diagram**

## **Test Access Port Registers**

| Register name          | Length   | Symbol     | Notes |

|------------------------|----------|------------|-------|

| Instruction register   | 3 bits   | IR [2:0]   |       |

| Bypass register        | 1 bits   | BP         |       |

| ID register            | 32 bits  | ID [31:0]  |       |

| Boundary scan register | 109 bits | BS [109:1] |       |

### **TAP Controller Instruction Set**

| IR2 | IR1 | IR0 | Instruction          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Notes   |

|-----|-----|-----|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 0   | 0   | 1   | EXTEST               | The EXTEST instruction allows circuitry external to the component package to be tested. Boundary scan register cells at output balls are used to apply test vectors, while those at input balls capture test results. Typically, the first test vector to be applied using the EXTEST instruction will be shifted into the boundary scan register using the PRELOAD instruction. Thus, during the Update-IR state of EXTEST, the output driver is turned on and the PRELOAD data is driven onto the output balls. The IDCODE instruction causes the ID ROM to be loaded into the ID register when the controller is in capture-DR mode and places the ID       | 1, 2, 3 |

|     |     |     |                      | register between the TDI and TDO balls in shift-DR mode. The IDCODE instruction is the default instruction loaded in at power up and any time the controller is placed in the Test-Logic-Reset state.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

| 0   | 1   | 0   | SAMPLE-Z             | If the SAMPLE-Z instruction is loaded in the instruction register, all RAM outputs are forced to an inactive drive state (high-Z), moving the TAP controller into the capture-DR state loads the data in the RAMs input into the boundary scan register, and the boundary scan register is connected between TDI and TDO when the TAP controller is moved to the shift-DR state.                                                                                                                                                                                                                                                                               | 3, 4    |

| 0   | 1   | 1   | RESERVED             | The RESERVED instructions are not implemented but are reserved for future use. Do not use these instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

| 1   | 0   | 0   | SAMPLE<br>(/PRELOAD) | When the SAMPLE instruction is loaded in the instruction register, moving the TAP controller into the capture-DR state loads the data in the RAMs input and I/O buffers into the boundary scan register. Because the RAM clock(s) are independent from the TAP clock (TCK) it is possible for the TAP to attempt to capture the I/O ring contents while the input buffers are in transition (i.e., in a metastable state). Although allowing the TAP to SAMPLE metastable input will not harm the device, repeatable results cannot be expected. Moving the controller to shift-DR state then places the boundary scan register between the TDI and TDO balls. | 3       |

| 1   | 0   | 1   | RESERVED             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| 1   | 1   | 0   | RESERVED             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| 1   | 1   | 1   | BYPASS               | The BYPASS instruction is loaded in the instruction register when the bypass register is placed between TDI and TDO. This occurs when the TAP controller is moved to the shift-DR state. This allows the board level scan path to be shortened to facilitate testing of other devices in the scan path.                                                                                                                                                                                                                                                                                                                                                        |         |

Notes: 1. Data in output register is not guaranteed if EXTEST instruction is loaded.

- 2. After performing EXTEST, power-up conditions are required in order to return part to normal operation.

- 3. RAM input signals must be stabilized for long enough to meet the TAPs input data capture setup plus hold time ( $t_{CS}$  plus  $t_{CH}$ ). The RAMs clock inputs need not be paused for any other TAP operation except capturing the I/O ring contents into the boundary scan register.

- 4. Clock recovery initialization cycles are required to return from the SAMPLE-Z instruction.

## **Boundary Scan Order**

| Ball ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |         | Signal names |    | s   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|--------------|----|-----|

| 1         6R         /C         /C         /C           2         6P         C         C         C           3         6N         SA         SA         SA           4         7P         SA         SA         SA           5         7N         SA         SA         SA           6         7R         SA         SA         SA           8         8P         SA         SA         SA           8         8P         SA         SA         SA           9         9R         SA         SA         SA           9         9                                                                                   | Bit # | Ball ID |              |    |     |

| 2         6P         C         C         C           3         6N         SA         SA         SA           4         7P         SA         SA         SA           5         7N         SA         SA         SA           6         7R         SA         SA         SA           8         8P         SA         SA         SA           9         9R         SA         SA         SA           10         11P         Q0         Q0         Q0           11         10P         D0         D0         D0                                                                                     |       |         |              |    |     |

| 3         6N         SA         SA         SA           4         7P         SA         SA         SA           5         7N         SA         SA         SA           6         7R         SA         SA         SA           7         8R         SA         SA         SA           8         8P         SA         SA         SA           9         9R         SA         SA         SA           10         11P         Q0         Q0         Q0           11         10P         D0         D0         D0           11         10P         D0         D0         D0           12         10N         NC         NC         D9           13         9P         NC         NC         Q9           14         10M         NC         Q1         Q1           15         11N         NC         NC         D10           17         9N         NC         NC         Q10           18         11L         Q1         Q2         Q2           19         11M         D1         D2         D2           <                                                                      |       |         |              |    |     |

| 4         7P         SA         SA         SA           5         7N         SA         SA         SA           6         7R         SA         SA         SA           7         8R         SA         SA         SA           8         8P         SA         SA         SA           9         9R         SA         SA         SA           10         11P         Q0         Q0         Q0           11         10P         D0         D0         D0           11         10P         D0         D0         D0           11         10P         D0         D0         D0           12         10N         NC         NC         D9           13         9P         NC         NC         Q9           14         10M         NC         NC         Q9           14         10M         NC         NC         D10           17         9N         NC         NC         D10           17         9N         NC         NC         D10           17         9N         NC         NC         NC                                                                                 |       |         |              |    |     |

| 5         7N         SA         SA         SA           6         7R         SA         SA         SA           7         8R         SA         SA         SA           8         8P         SA         SA         SA           9         9R         SA         SA         SA           10         11P         Q0         Q0         Q0           11         10P         D0         D0         D0           11         10P         D0         D0         D0           11         10P         D0         D0         D0           12         10N         NC         NC         D9           13         9P         NC         NC         Q9           14         10M         NC         NC         Q9           14         10M         NC         NC         Q9           14         10M         NC         NC         Q1           15         11N         NC         NC         Q10           17         9N         NC         NC         Q10           18         11L         Q1         Q2         Q2                                                                              |       |         |              |    |     |

| 6         7R         SA         SA         SA           7         8R         SA         SA         SA           8         8P         SA         SA         SA           9         9R         SA         SA         SA           10         11P         Q0         Q0         Q0           11         10P         D0         D0         D0           11         10P         D0         D0         D0           11         10P         D0         D0         D0           12         10N         NC         NC         D9           13         9P         NC         NC         Q9           14         10M         NC         NC         D1           15         11N         NC         D1         D1           16         9M         NC         NC         D10           17         9N         NC         NC         Q10           18         11L         Q1         Q2         Q2           20         9L         NC         NC         D11           21         10L         NC         NC         D11                                                                            |       |         |              |    |     |

| 7         8R         SA         SA         SA           8         8P         SA         SA         SA           9         9R         SA         SA         SA           10         11P         Q0         Q0         Q0           11         10P         D0         D0         D0           11         10P         D0         D0         D0           12         10N         NC         NC         D9           13         9P         NC         NC         D9           14         10M         NC         NC         Q9           14         10M         NC         NC         Q9           14         10M         NC         NC         D10           15         11N         NC         NC         D10           16         9M         NC         NC         D10           17         9N         NC         NC         D10           17         9N         NC         NC         D10           18         11L         Q1         Q2         Q2           19         11M         D1         D2         D2                                                                         |       |         |              |    |     |

| 8         8P         SA         SA         SA           9         9R         SA         SA         SA           10         11P         Q0         Q0         Q0           11         10P         D0         D0         D0           12         10N         NC         NC         D9           13         9P         NC         NC         Q9           14         10M         NC         Q1         Q1           15         11N         NC         D1         D1           16         9M         NC         NC         D10           17         9N         NC         NC         D10           17         9N         NC         NC         D10           17         9N         NC         NC         D10           18         11L         Q1         Q2         Q2           19         11M         D1         D2         D2           20         9L         NC         NC         D11           21         10L         NC         NC         D11           22         11K         NC         NC         NC         D12 <td></td> <td></td> <td></td> <td></td> <td></td>          |       |         |              |    |     |

| 9         9R         SA         SA         SA           10         11P         Q0         Q0         Q0           11         10P         D0         D0         D0           12         10N         NC         NC         D9           13         9P         NC         NC         Q9           14         10M         NC         Q1         Q1           15         11N         NC         D1         D1           16         9M         NC         NC         D10           17         9N         NC         NC         Q10           18         11L         Q1         Q2         Q2           19         11M         D1         D2         D2           20         9L         NC         NC         Q11           21         10L         NC         NC         D11           21         10L         NC         NC         Q11           22         11K         NC         Q3         Q3           23         10K         NC         D3         D3           24         9J         NC         NC         Q12      <                                                              |       |         |              |    |     |

| 10         11P         Q0         Q0         Q0           11         10P         D0         D0         D0           12         10N         NC         NC         D9           13         9P         NC         NC         Q9           14         10M         NC         Q1         Q1           15         11N         NC         D1         D1           16         9M         NC         NC         D10           17         9N         NC         NC         Q10           18         11L         Q1         Q2         Q2           19         11M         D1         D2         D2           20         9L         NC         NC         Q11           21         10L         NC         NC         D11           21         10L         NC         NC         Q11           22         11K         NC         Q3         Q3           23         10K         NC         D3         D3           24         9J         NC         NC         D12           25         9K         NC         NC         D12                                                                   |       |         |              |    |     |

| 11         10P         D0         D0         D0           12         10N         NC         NC         D9           13         9P         NC         NC         Q9           14         10M         NC         Q1         Q1           15         11N         NC         D1         D1           16         9M         NC         NC         D10           17         9N         NC         NC         Q10           18         11L         Q1         Q2         Q2           19         11M         D1         D2         D2           20         9L         NC         NC         Q10           18         11L         Q1         Q2         Q2           20         9L         NC         NC         D11           21         10L         NC         NC         D11           21         10L         NC         NC         Q11           22         11K         NC         Q3         Q3           23         10K         NC         D3         D3           24         9J         NC         NC         Q12                                                                   |       |         |              |    |     |

| 12         10N         NC         NC         D9           13         9P         NC         NC         Q9           14         10M         NC         Q1         Q1           15         11N         NC         D1         D1           16         9M         NC         NC         D10           17         9N         NC         NC         Q10           18         11L         Q1         Q2         Q2           19         11M         D1         D2         D2           20         9L         NC         NC         Q10           18         11L         Q1         Q2         Q2           20         9L         NC         NC         D10           20         9L         NC         NC         D11           21         10L         NC         NC         D11           21         10L         NC         NC         Q11           22         11K         NC         Q3         Q3           23         10K         NC         NC         D12           25         9K         NC         NC         Q12                                                                  |       |         |              |    |     |